-

목차

반응형1. J-K 플립플롭

J-K 플립플롭은 1비트의 정보를 저장할 수 있는 디지털 전자 회로의 한 종류입니다.

S-R 플립플랍의 향상된 기능으로 추가 입력 및 기능을 제공합니다.

J-K 플립플랍에는 J(세트)와 K(리셋)의 두 가지 입력과 Q 및 Q̅(Q 보어)의 두 가지 출력이 있습니다.

J-K 플립플롭은 또한 두 개의 교차 결합 NAND 게이트 또는 두 개의 교차 결합 NOR 게이트를 사용하여 구성됩니다.

우리가 NAND 게이트를 사용하여 J-K 플립플랍을 제작한다고 가정해 보겠습니다.

처음에는 J와 K가 모두 낮으면 두 NAND 게이트의 두 입력이 모두 높고 두 출력이 모두 낮습니다.

Q 출력은 낮고 Q 출력은 높습니다. 클럭 신호가 플립플랍에 적용되면 J 및 K 입력이 적용될 수 있습니다.

J가 높고 K가 낮으면 첫 번째 NAND 게이트의 출력이 낮아져 두 번째 NAND 게이트의 입력이 높아져서 출력이 낮아집니다.

이렇게 하면 Q 출력이 하이로, Q 출력이 로우로 전환되어 플립플롭이 설정됩니다.

마찬가지로, K가 높고 J가 낮으면 두 번째 NAND 게이트의 출력이 낮아지므로 첫 번째 NAND 게이트의 입력이 높아져서 출력이 낮아집니다.

이렇게 하면 Q 출력이 낮아지고 Q̅ 출력이 높아져 플립플롭이 재설정됩니다.

J-K 플립플롭에는 J와 K가 모두 높을 경우 첫 번째 NAND 게이트의 출력이 반대 상태로 전환되어 두 번째 NAND 게이트의 출력도 전환되는 추가 기능이 있습니다.

즉, J-K 플립플롭이 현재 상태에서 반대 상태로 전환됩니다.

예를 들어 Q 출력이 현재 높으면 낮음으로 가고, 현재 낮으면 높음으로 갑니다. 전환 기능은 주파수 분할기, 시프트 레지스터 및 카운터와 같은 애플리케이션에서 유용합니다.

2. D 플립플롭

D 플립플롭은 1비트의 정보를 저장할 수 있는 디지털 전자 회로의 한 종류입니다.

데이터 입력을 저장하고 한 클럭 주기만큼 지연시키기 때문에 "데이터" 또는 "지연" 플립플롭이라고도 합니다.

D 플립플롭에는 입력 1개, D(데이터), 클럭 입력 1개, 출력 2개, Q 및 Q̅(Q 보완)이 있습니다.

D 플립플롭은 두 개의 NAND 게이트 또는 두 개의 NOR 게이트를 사용하여 구성되며, 출력은 서로 반대되는 입력에 교차 결합됩니다.

NAND 게이트를 사용하여 D 플립플랍을 구축한다고 가정합니다.

처음에는 두 NAND 게이트의 두 입력이 모두 높으면 두 출력이 모두 낮습니다.

Q 출력은 낮고 Q 출력은 높습니다. 클럭 신호가 플립플랍에 적용되면 입력 D가 활성화될 수 있습니다.

D가 높으면 첫 번째 NAND 게이트의 출력이 낮아져 두 번째 NAND 게이트의 입력이 높아져 출력이 낮아집니다.

이렇게 하면 Q 출력이 높아지고 Q 출력이 낮아져 데이터 입력 D가 저장됩니다.

반면에, D가 낮으면 첫 번째 NAND 게이트의 출력이 높게 유지되고, 두 번째 NAND 게이트의 입력이 낮게 유지되어 출력이 높게 유지됩니다.

이렇게 하면 Q 출력은 로우로, Q 출력은 하이로, 데이터 입력 D̅(D의 보어)가 저장됩니다.

D 플립플롭은 메모리 저장, 데이터 전송 및 클럭 동기화와 같은 애플리케이션에 유용합니다.

일반적으로 레지스터 및 카운터와 같은 보다 복잡한 회로의 구성 요소로 사용됩니다.

3. D 래치

D 래치는 D 플립플랍과 유사하게 1비트의 정보를 저장할 수 있는 디지털 전자 회로의 한 유형입니다.

또한 "투명 래치" 또는 "데이터 래치"라고도 하는데, 이는 클럭 신호에 관계없이 출력 Q가 입력 D를 지속적으로 반사하기 때문입니다.

D 래치에는 하나의 입력, D(데이터), 하나의 클럭 입력 및 하나의 출력 Q가 있습니다.

D 래치는 두 개의 NAND 게이트 또는 두 개의 NOR 게이트를 사용하여 구성되며, 출력은 서로 반대되는 입력에 교차 결합되며, 래치의 투명도를 제어하는 활성화 입력이라는 추가 입력이 사용됩니다.

NAND 게이트를 사용하여 D 래치를 구축한다고 가정합니다.

처음에는 두 NAND 게이트의 두 입력이 모두 높으면 두 출력이 모두 낮습니다.

Q 출력은 낮고 Q 출력은 높습니다. 활성화 입력이 높으면 D 입력이 적용될 수 있습니다.

D가 높으면 첫 번째 NAND 게이트의 출력이 낮아져 두 번째 NAND 게이트의 입력이 높아져 출력이 낮아집니다.

이렇게 하면 Q 출력이 높아지고 Q 출력이 낮아져 데이터 입력 D가 저장됩니다.

반면에, D가 낮으면 첫 번째 NAND 게이트의 출력이 높게 유지되고, 두 번째 NAND 게이트의 입력이 낮게 유지되어 출력이 높게 유지됩니다.

이렇게 하면 Q 출력은 로우로, Q 출력은 하이로, 데이터 입력 D̅(D의 보어)가 저장됩니다.

활성화 입력이 낮으면 D 래치가 투명해지고 출력 Q는 클럭 신호에 관계없이 입력 D를 계속 반사합니다.

즉, 클럭 신호가 낮더라도 입력 D에 따라 출력 Q가 변경될 수 있습니다. D 래치는 데이터 전송, 레지스터 스토리지 및 제어 시스템과 같은 애플리케이션에 유용합니다.

일반적으로 시프트 레지스터 및 멀티플렉서와 같은 보다 복잡한 회로를 위한 빌딩 블록으로 사용됩니다.

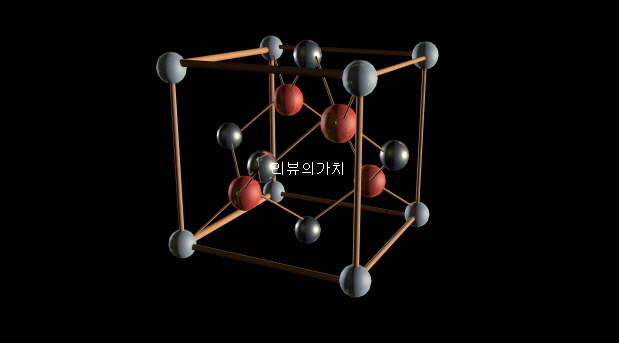

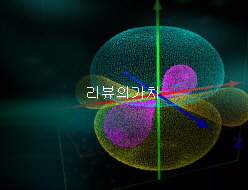

<플립플롭>

<플립플롭>

<플립플롭>

<플립플롭>

<플립플롭>

<플립플롭>

<플립플롭>

<플립플롭>

<플립플롭> 반응형

리뷰의 가치

100% 내돈내산 제품만 리뷰합니다.